您當(dāng)前的位置:檢測(cè)資訊 > 科研開(kāi)發(fā)

嘉峪檢測(cè)網(wǎng) 2025-03-14 08:51

各位芯片行業(yè)的朋友們,今天,我想結(jié)合相關(guān)資料和最新研究,和大家聊聊FinFET技術(shù)中常見(jiàn)的失效分析(FA)問(wèn)題、可靠性問(wèn)題以及相應(yīng)的定位方法。

一、FinFET簡(jiǎn)介

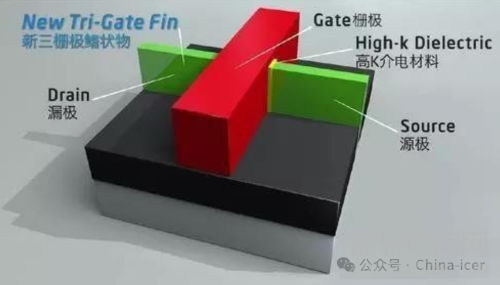

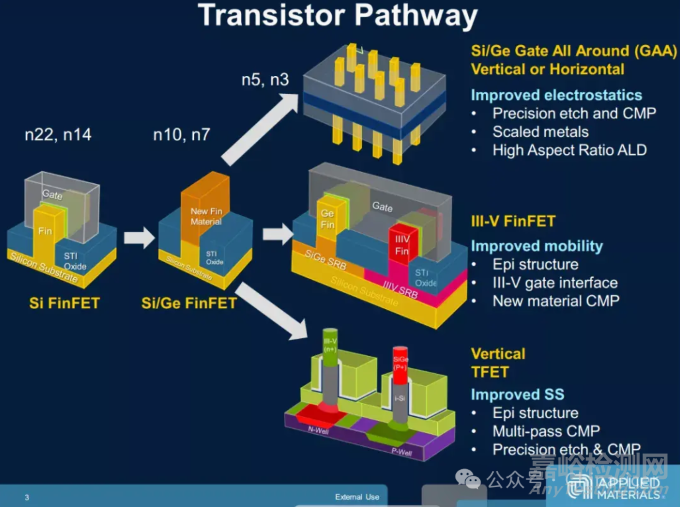

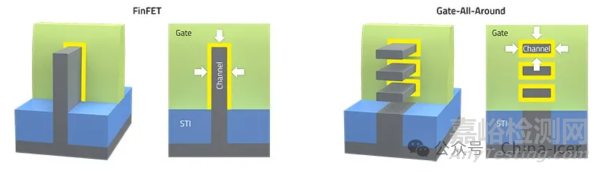

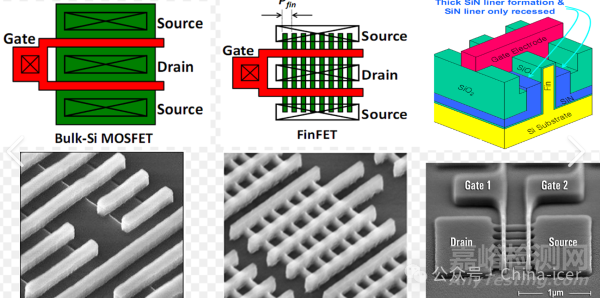

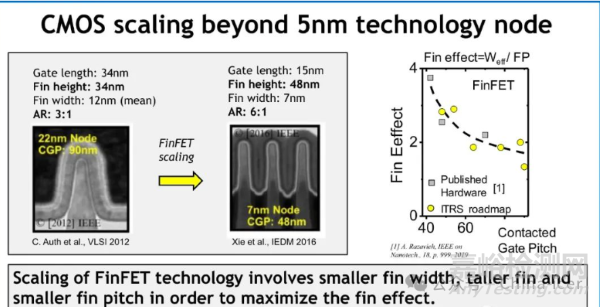

FinFET(鰭式場(chǎng)效應(yīng)晶體管)是一種新型的Transistor結(jié)構(gòu),它通過(guò)在傳統(tǒng)planner 結(jié)構(gòu)上引入3D Fin結(jié)構(gòu),大大提高了Transistor的性能和集成度,在現(xiàn)代芯片制造中得到了廣泛應(yīng)用。然而,隨著工藝節(jié)點(diǎn)的不斷縮小,F(xiàn)inFET也面臨著一系列的FA和可靠性挑戰(zhàn)。

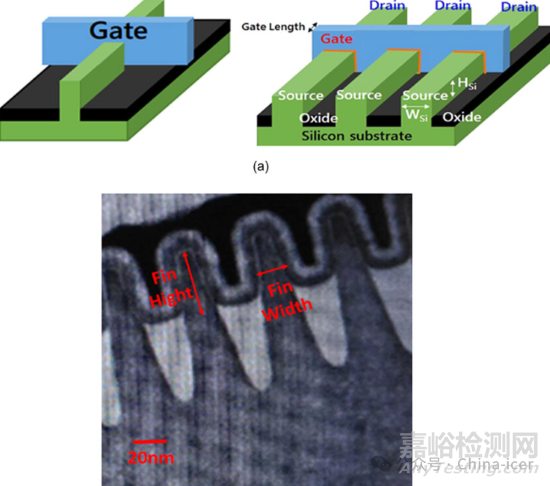

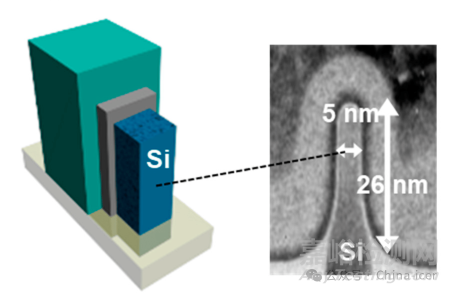

很多人后臺(tái)私信我,哪里是Fin Width和Fin Hight,這里放張圖,解釋一下

FinFET/Planar工藝對(duì)比表

|

Loop |

Planar |

FinFET |

|

AA |

Single pattern STI |

SADP,F(xiàn)in etch,Cut,SDB |

|

Poly Gate |

P1+P2 |

Poly CMP+ Line+Cut |

|

EPI |

SiGe/SiC |

SiP/SiGe/low-K spacer |

|

RMG |

Single pattern |

Single pattern+self-align contact |

|

MEOL |

Single pattern |

M0 AA/M0 Gate/Cut block |

|

Metal |

Single pattern |

LELE |

二、常見(jiàn)的FinFET FA問(wèn)題

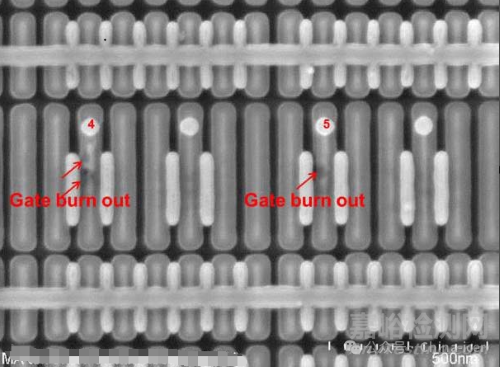

(一)Gate related issue

As we all known,Gox Integrity 是一個(gè)Key issue。Gox過(guò)薄可能會(huì)導(dǎo)致Leakage current增加,影響T的開(kāi)關(guān)性能。此外,Gate material與Fin之間的界面質(zhì)量也會(huì)影響器件的性能,如 interface states密度過(guò)高會(huì)導(dǎo)致載流子 μ 遷移率下降。

(二)Fin related issue

Fin size和形狀對(duì)FinFET的性能有重要影響。Fin height ,F(xiàn)in width non - uniform會(huì)導(dǎo)致device parameters的non - uniform,進(jìn)而影響芯片的整體性能。另外,F(xiàn)in surface的粗糙度也會(huì)影響carrier的傳輸,增加電阻。

(三)SD related issue

SD的摻雜濃度和分布不均勻會(huì)導(dǎo)致Transistor 的閾值電壓漂移,影響器件的穩(wěn)定性。同時(shí),SD與Fin之間的接觸電阻過(guò)大也會(huì)降低器件的性能。

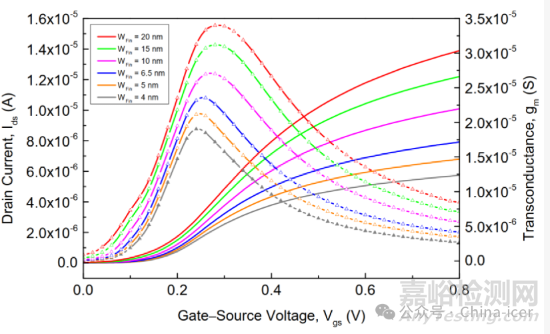

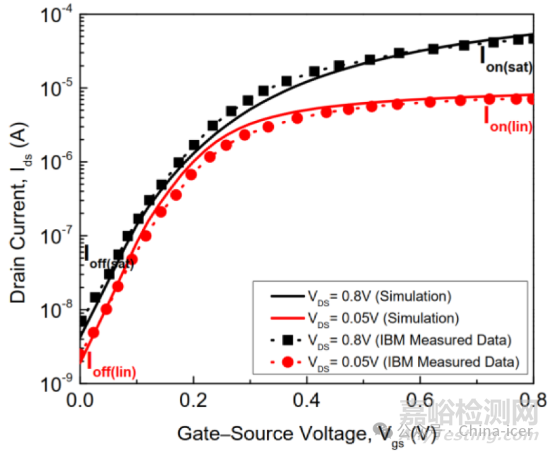

Simulation and experimental I–V curves of the investigated FinFET model

三、常見(jiàn)的FinFET Rel Issue

FinFET 可靠性問(wèn)題是復(fù)雜的二維問(wèn)題, 可靠性問(wèn)題類(lèi)似,

(一)HCI

HCI是FinFET中常見(jiàn)的可靠性問(wèn)題之一。在高電場(chǎng)作用下,Carrier獲得足夠的能量注入到柵極氧化層中,導(dǎo)致Gox trapped charge增加,從而引起Threshold voltage thift和Gm down,影響device的性能和壽命。

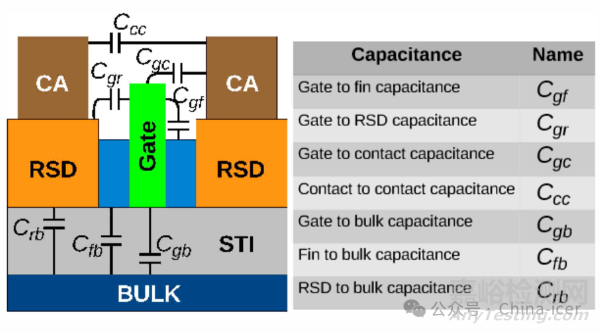

FinFET Parasitic Capacitance Model

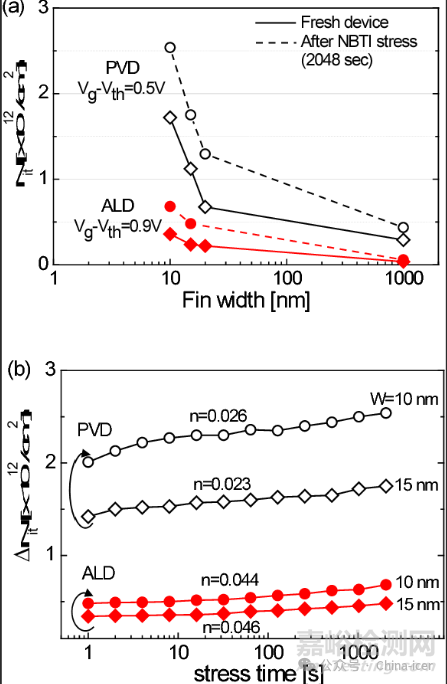

(二)NBTI

NBTI主要發(fā)生在P型FinFET中。在負(fù)偏壓和高溫條件下,Gox與Si interf. 處會(huì)產(chǎn)生defect,導(dǎo)致Gox drift Positive,降低器件的驅(qū)動(dòng)能力。

(三)EM

隨著芯片集成度的提高,金屬互連線(xiàn)中的電流密度增大,EM 問(wèn)題變得更加突出。EM 會(huì)導(dǎo)致金屬互連線(xiàn)中的原子遷移,形成 Void 或Short,影響芯片的可靠性。

4)known unkonw Issue?

太多,人類(lèi)已知知<<知道的知識(shí)

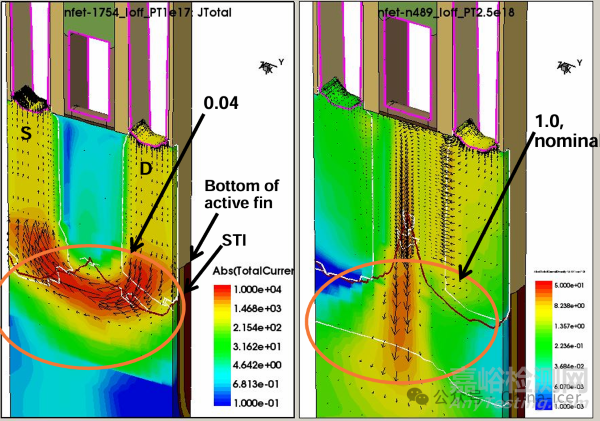

最典型的我約到 doping導(dǎo)致 leakage,可以仿真無(wú)法探測(cè)

TCAD plot

再有就是量子力學(xué)的問(wèn)題

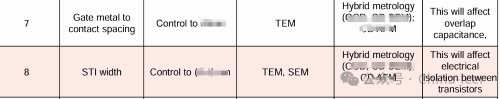

四、FinFET問(wèn)題的定位方法

(一)電性測(cè)試定位

通過(guò)對(duì)芯片進(jìn)行各種電性測(cè)試,如I - V特性測(cè)試、C - V特性測(cè)試等,可以初步判斷問(wèn)題所在的區(qū)域。例如,如果某個(gè)Transistor的漏電流異常增大,可能是柵極氧化層存在問(wèn)題。

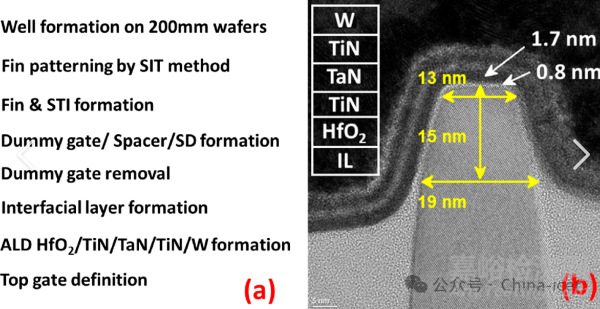

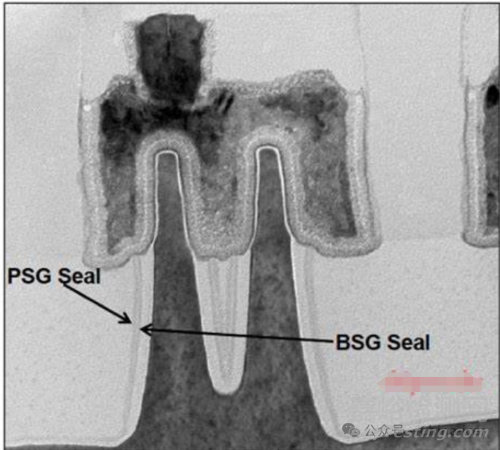

(二)物理分析定位

利用SEM、TEM等設(shè)備對(duì)芯片進(jìn)行物理分析,可以直觀(guān)地觀(guān)察IC的微觀(guān)結(jié)構(gòu)和缺陷。例如,通過(guò)TEM可以觀(guān)察到Gate OX的厚度和質(zhì)量,以及Fin的尺寸和形狀。

TEM image

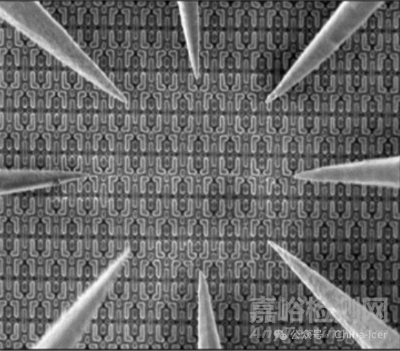

(三)失效分析技術(shù)

常用的失效分析技術(shù)包括微OBIRCH、Emmi、LCT、Nano-probe、SIL等。這些技術(shù)可以檢測(cè)到芯片中的漏電點(diǎn)和熱點(diǎn),幫助定位失效位置。例如,OBIRCH可以通過(guò)檢測(cè)芯片表面的光反射變化來(lái)定位漏電點(diǎn)。

Nanoprobe

因?yàn)槲业谋尘笆菑男酒馁|(zhì)量失效分析可靠性,之后轉(zhuǎn)到了流程質(zhì)量,過(guò)程質(zhì)量、SQE, TQM, 所有對(duì)這個(gè)有些涉獵

FinFET的質(zhì)量控制

會(huì)根據(jù) Fin Height variation, Fin width variation

Fin With variation (脫敏版)

以及對(duì)測(cè)量方法, 質(zhì)量管控、要求,有專(zhuān)項(xiàng)要求

五、總結(jié)

FinFET技術(shù)在提高芯片性能和集成度方面具有巨大優(yōu)勢(shì),但也面臨著諸多FA和可靠性問(wèn)題。作為芯片質(zhì)量管理人員,我們需要深入了解這些問(wèn)題,了解要求的來(lái)源, 并掌握有效的定位方法,以確保芯片的質(zhì)量和可靠性。希望今天的分享能對(duì)大家有所幫助,讓我們一起為芯片行業(yè)的發(fā)展貢獻(xiàn)力量!

最近有個(gè)別同志舉報(bào)我違反原創(chuàng), 導(dǎo)致我被平臺(tái)警告和屏蔽, 國(guó)內(nèi)最新的材料不多, 發(fā)文獻(xiàn)前我也比較謹(jǐn)慎, 只能保證不是為盈利為目的為目的的分享。 也希望高抬貴手。

來(lái)源:芯芯有我